- 您现在的位置:买卖IC网 > Sheet目录1990 > CDP68HC68T1M (Intersil)IC RTC 32X8 NVSRAM CMOS 20-SOIC

5

FN1547

.8

October

29,

200

7

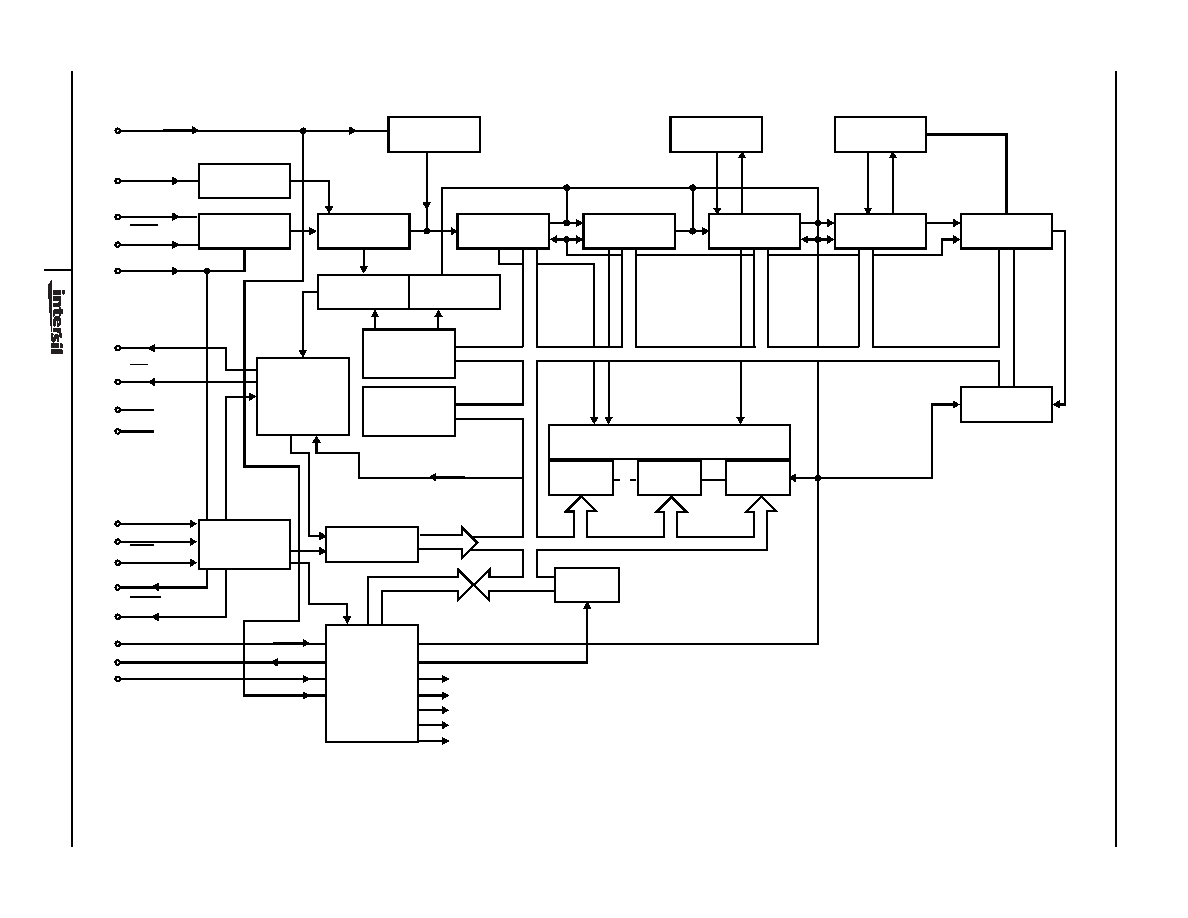

Functional Block Diagram

FREEZE

CIRCUIT

CE

LINE

50/60Hz

AM - PM AND

HOUR LOGIC

DAY/DAY

OF WEEK

OSCILLATOR

XTAL IN

XTAL OUT

VBATT

PRESCALE

SECOND

MINUTE

HOUR

CALENDAR

LOGIC

MONTH

PRESCALE

SELECT

CLOCK

SELECT

CLOCK

CONTROL

REGISTER

INTERRUPT

CONTROL

REGISTER

CLOCK

AND

INT

LOGIC

CLOCK

OUT

INT

VDD

VSS

POWER

SENSE

CONTROL

INT STATUS

REGISTER

LINE

PSE

VSYS

POR

CPUR

SCK

MISO

MOSI

COMPARATOR

SECOND

LATCH

MINUTE

LATCH

HOUR

LATCH

32x8

RAM

SERIAL

INTERFACE

YEAR

8-BIT DATA BUS

FIGURE 1. REAL TIME CLOCK FUNCTIONAL DIAGRAM

CDP68HC68T1

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CPLL66-1600-2200

IC VCO PLL/SYNTH 2.2GHZ SMD

CPLL66-2175-2175

IC VCO PLL/SYNTH 2175MHZ SMD

CPLL66-2400-2500

IC VCO PLL/SYNTH 2500MHZ SMD

CPLL66-2450-2450

IC VCO PLL/SYNTH 2450MHZ SMD

CPLL66-3160-3380

IC VCO PLL/SYNTH 3380MHZ SMD

CPLL66-3475-3475

IC VCO PLL/SYNTH 3475MHZ SMD

CPLL66-4160-4380

IC VCO PLL/SYNTH 4380MHZ SMD

CPLL66-4240-4240

IC VCO PLL/SYNTH 4240MHZ SMD

相关代理商/技术参数

CDP68HC68T1M2

功能描述:实时时钟 PERIPH SPIAL-TIME- CLK 16W IND RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M296

功能描述:实时时钟 PERIPH SPIAL-TIME- CLK 16W INDEL RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M296S2357

制造商:Rochester Electronics LLC 功能描述:- Bulk

CDP68HC68T1M2Z

功能描述:实时时钟 PERI SPIAL-TIME-CLK RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M2Z96

功能描述:实时时钟 PERI SPIAL-TIME-CLK RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M96

功能描述:实时时钟 PERIPH SPIAL-TIME- CLK 20W INDEL RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

CDP68HC68T1M96S2357

制造商:Rochester Electronics LLC 功能描述:- Bulk

CDP68HC68T1MZ

功能描述:实时时钟 W/ANEAL PERIPH SPIAL -TIME-CLK 20W IND RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube